還記得在去年 10 月就有媒體分享台積電將於去年年底的國際電子元件會議(International Electron Devices Meeting, IEDM)報告二維材料邏輯元件的開發成果,算是半導體元件開發的重大突破。

這些研究的其中一位領導人物,Dr. Iuliana Radu,其實也在 2021 年底發表了一篇她於 imec 研究的《在晶圓規模下,使用二維材料製作高效能運算邏輯電路時會遇到的製程整合挑戰》論文:Challenges of Wafer-Scale Integration of 2D Semiconductors for High-Performance Transistor Circuits。Dr. Radu 目前是台積電技術研究部門(Corporate Research)的副處長(Deputy Director)。她過去在 imec 做了約八年的研究,現在這篇網誌文章就是在談她作為第三作者於 2021 年底發表的技術論文。

雖然這篇論文是在 imec 完成的,但由於其第三作者 Dr. Radu 在論文投稿時就已在台積電服務,並且她也在一年後代表台積電於 IEDM 發表了二維材料研發進展論文,所以我認為這篇論文還是有一定程度的代表性,這也是我想分享這篇論文的主因。

接下來我將先跟大家簡略回顧 IEDM 官網上公開的 TSMC 二維材料研究進展,然後再分享上述那篇 imec 論文的中文翻譯(該論文以 CC 4.0 授權分享)。但因為時間有限,而且這篇論文非常長,所以我只翻了前兩節的內容。

台積電的 IEDM 論文報告

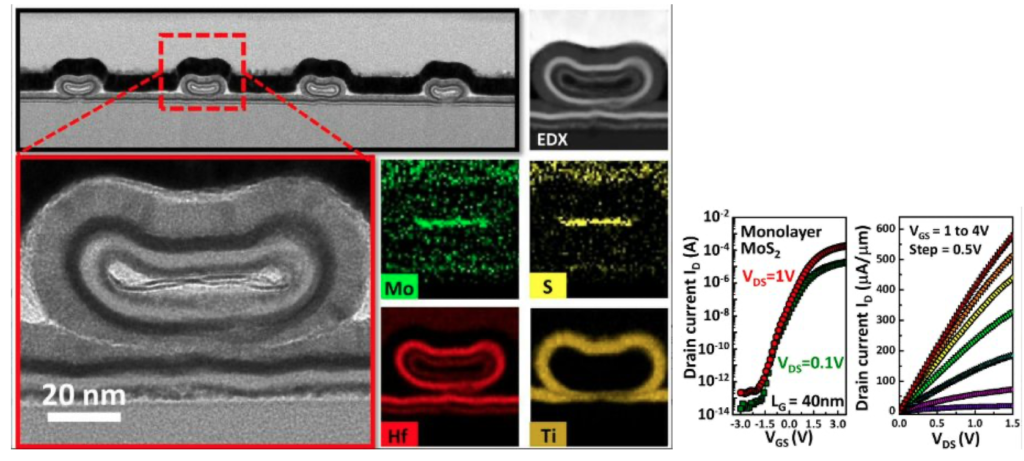

一、成功將 HfO2-based dielectrics 藉由原子層沉積(ALD)技術沉積到單原子層材料 MoS2 上,做出一個等效氧化層厚度 (EOT) 1nm,而實際厚度 3.4nm 的 top-gated nFET。其次臨界擺幅可達近乎理想的 <70 mV/dec。

IEDM Paper 7.4 Nearly Ideal Subthreshold Swing in Monolayer MoS2 Top-Gate nFETs with Scaled EOT of 1nm)

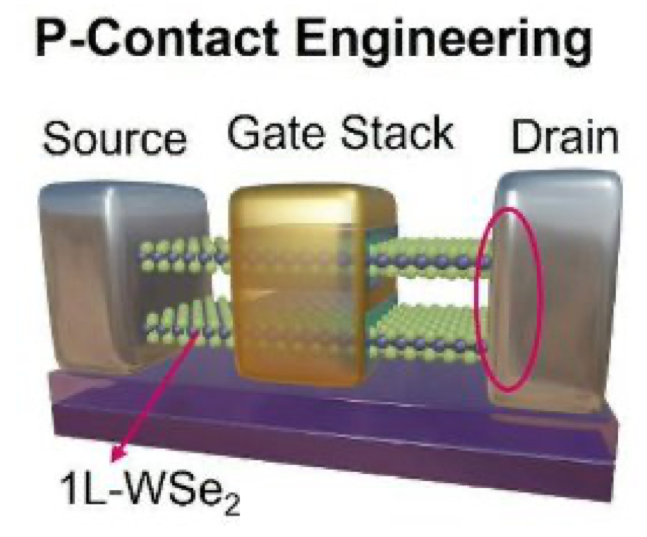

二、成功找到適合給 P 型二維材料作為低電阻電極的材料——名為 1T-TiS2 的凡德瓦金屬(van der Waals metallic contacts),以及使用多種材料組合而成的“半金屬”電極(semimetallic contacts),像是 Co3Sn2S2,其理論電阻可低至 20 Ω·μm。

IEDM Paper 28.1 Computational Screening and Multiscale Simulation of Barrier-Free Contacts for 2D Semiconductor pFETs

三、成功以厚度約為 0.7nm 的二維材料 MoS2 開發出環繞式閘極(GAA)奈米薄板場效電晶體(nanosheet FET),閘極長度約 40nm,電流密度約 410 µA/µm at $V_\text{DS}=1(V)$,$I_\text{on}/I_\text{off}>10^8$、$V_\text{TH}=1.4(V)$ 並且幾乎沒有 DIBL。

IEDM Paper 34.5 First Demonstration of GAA Monolayer-MoS2 Nanosheet nFET with 410 μA/μm ID at 1V VD at 40nm Gate Length

二維材料邏輯元件晶圓級(Wafer-scale)製程挑戰

Challenges of Wafer-Scale Integration of 2D Semiconductors for High-Performance Transistor Circuits

作者:Tom Schram, Surajit Sutar, Iuliana Radu, Inge Asselberghs

摘要(Abstract)

就目前來說,二維材料通常是用來作為光感應器,或是在後段製程(BEOL)與晶片整合在一起以添加一些特殊功能。至於直接將二維材料做為高效能電路的邏輯元件,就應該要等到 Si-based CFET 量產後才可能推出。

這篇論文將針對前述的高效能應用,以在實際晶圓廠量產為前提(而非在理想的實驗室環境),分析在整片晶圓上製作二維材料邏輯元件的製程開發現況與挑戰。雖然常見的二維材料的測試元件(Test vehicles)都是以在實驗室中的理想環境製作而成的“單片”奈米薄板元件(Single-sheet devices),但其實,現在的技術已能在晶圓廠裡大規模製作了。這篇論文將會回顧這些晶圓廠製程模組的開發現況,像是該如何建構與實際晶圓廠製程環境相容的單片(Single-sheet)二維元件製程。

雖然許多極具關鍵的製程模組仍有待進一步開發,但我們已在許多製程方面有所進展,像是該如何以 MX2 二維材料製作載子通道、該如何沈積 high-k 介電材料以及製作金屬電極。最後也會談談可用以進一步微縮“堆疊式(多片)奈米薄板元件”(ultra-scaled stacked nanosheets)的可能製程。

1. 前言(Introduction)

由於矽通道(Si-channel)在閘極長度達到 18nm 時就已達到其性能極限,所以我們得開始在元件設計、材料工程、電路與系統最佳化等方面思考,究竟該如何突破當前困境。而且這些方法還得有足夠的創意才可能帶來真正的突破,像是引入鰭式場效電晶體(FinFET)、奈米薄板電晶體(nano-sheet FET)以及叉式薄板電晶體(Fork-sheet FET)。

對於閘極長度 10nm 以下的矽元件(Si-based devices),因為已經很難精準開關這種元件的電流通道,所以已經越來越難微縮下去了。要做到如此短的閘極長度,其矽通道的厚度就必須小於 5 奈米才有可能。然而,不論是製程本身不經意與矽通道起的化學反應,還是如此薄的矽通道的電性本身就很難控制,這一切都使得「矽通道微縮」難上加難。

如今,被公認為可用以延續半導體技術發展的主要候選材料為,具有半導體性質的二維材料(semiconducting 2D materials),這些材料也被稱為「凡德瓦薄膜材料」(van der Waals layered materials)。這種二維材料只有幾個原子厚,而且表面相當穩定,難以起化學反應,這使我們相對容易控制於其內部形成的載子通道。每層二維材料的厚度通常不超過一奈米。

在各種二維材料中,石墨烯(graphene)是被研究得最為深入的一種材料。雖然它因為沒有能隙(band gap)而難以作為電晶體,但它有著許多相當適合在光學方面有所應用的材料性質,像是極佳的載子遷移率,以及由其獨特的狄拉克錐(Dirac cone)能帶結構而帶來的、可輕易由閘極調控濃度的載子特性。因此,石墨烯以及其他相關的二維材料大多都能夠用在感應器或是其他光電子元件上。這些應用通常都用到所謂的「混合」製程(hybrid integration)。首先是將矽元件做在晶片底部,然後在將這些二維材料元件做在晶片的最上層。而那些位於底部的矽元件就能用以提供晶片所需的驅動電流與輸出電路(read-out circuitry)。大部分這種混合製程——尤其是在晶片級製程裡(full-wafer integration)——通常都是使用剝離(lift-off)製程來製作接觸電極(contact)與閘極的微影成形(gate patterning)。使用剝離製程的好處是我們不需要在次奈米(sub-1 nm)二維材料上使用高選擇性蝕刻(highly selective etches),而且也因為感光元件通常有著比較大的特徵尺寸(feature size),所以只要我們使用低溫金屬製程,那就可以採用剝離(lift-off)製程了。

不過,我們這裡的討論重點在於該如何用二維材料取代高效能(high-performance)邏輯應用裡的矽元素(Si),而非取代感光元件裡的矽元素。由於適合作為高效能運算晶片的材料導電性質、能隙與載子遷移率等性質要求其實並不少,也不容易達成,所以實際上我們能選的二維材料也不多。而在所有二維材料中,目前最備受關注並被認為可用於製作高效能電晶體上的二維材料為黑磷(black phosphorus),以及由過渡金屬原子 M(例如,鉬 Mo 與鎢 W )以及氧族(chalcogen)元素 X 組成的 MX2 型態的過渡金屬硫化物(Transition Metal Dichalcogenides ; TMDC)。

由於黑磷對其周圍環境相當敏感,非常的不穩定,所以使得相對穩定的 MX2 二維材料成為的高效能電晶體研究對象。以目前來說,大部分具有代表性的二維材料元件——尤其是那些性能特別好的——通常都是在實驗室裡所製作完成的,而且都採用了局部的薄片搬移技術(local flake transfer)以及特製的電子束打印技術(e-beam printing)。然而,這些技術並不總是與晶圓廠的晶圓級製程相容,即便他們的確相當有助於向人們展示——以 MX2 為基礎的——二維材料電晶體的效能潛力。而且,相較於石墨烯,其實我們非常不確定究竟——適合用於石墨烯感光元件的——剝離製程(lift-off)是否能可靠穩定的整合進 MX2 二維材料製程裡頭,尤其是在我們要往小於 10nm 的特徵尺寸開發的時候,即便我們知道剝離法能用在較大的特徵尺寸上。最後,槽溝金屬的先進製程(advanced trench metallization)往往都需要的高溫環境,也使我們不太可能採用剝離製程。

我們先前已有展示且報告過在 300-mm 晶圓上製作二維材料邏輯元件的製程[7][8],而其中並沒有用到剝離製程。現在,我們想跟各位報告的製程,則是採用了較為傳統的「嵌入法」製程(damascene process)以製作金屬電極(contact and gate process)。雖然說,由於大面積元件的閘極很可能在化學機械研磨(CMP)的過程中被剝落下來的緣故,這製程很可能不適合用在面積大於幾個平方微米的元件,不過這製程基本上能應用在較小面積的元件上。

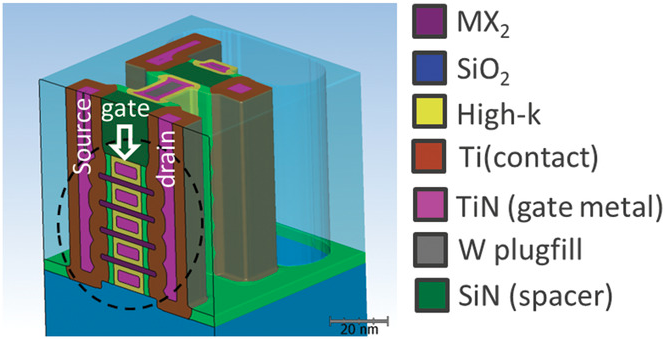

首先讓我們假設,以矽為基礎的堆疊式奈米薄片(Si-based stacked nanosheets)中的矽通道能夠被 MX2 二維材料通道所取代。基本上,我們預期在前者量產之後,人們就會開始引入以 MX2 二維材料為基礎的堆疊式奈米薄片電晶體(MX2-based stacked nanosheets FETs)。

而不論是以什麼材料為主的元件,我們總是能透過「堆疊」這些電流通道薄板——或是說薄片——來加大電流通道的有效寬度,使我們能在同樣的印刷版面積下(footprint)獲得更大的電流。在這份報告中,金屬接線的週期距離(metal pitch)以及閘極長度(gate length)分別為 16 與 14 奈米。我們預期,我們的二維材料元件除了有著更好的短通道效應,其極薄的載子通道也有著較微弱的寄生電容,從而有著更明顯提升的元件效能。

圖一為以二維材料為基礎的堆疊式反相器(inverter)的製程仿真示意圖,其中有四層 MX2。而為了更清楚地顯示 MX2 二維材料,其厚度被設定為 2 奈米,而非此研究中採用的真實二維材料(二硫化鎢,WS2)的 0.7 奈米。下一節會描述我們在整片晶圓上製作二維材料元件的製程整合,解釋目前尚待解決的困難,以及討論可能的解決之道。而最後一節則是討論,倘若要以二維材料取代矽,那麼究竟該朝向什麼方向去研發才比較可能有所幫助。

2. 在整片晶圓上製作“單片”奈米薄板二維材料電晶體的製程整合介紹(Wafer-Scale Integration of Single-Sheet 2D)

雖然我們的最終目標是「堆疊式」的二維材料奈米薄板電晶體,但我們其實可以從「單片」製程,來評估「堆疊」製程整合議題——因為單片與多片的初期製程考量其實差不多。除此之外,較為單純的「單片」製程也能大幅縮短最佳化製程所需的開發時間。

首先最為需要處理的問題是,我們應該採用什麼二維材料?除了要考慮其黏性、沈積製備方法以及對應高介電係數的絕緣材料選擇(high-k dielectrics)以外,我們也得考慮到 300mm 前段製程晶圓廠中的常見設備要求:大部分的機台都得能夠用在各種類型的晶片製程。雖然最終量產時難免會有些機台是專門為該製程量身打造調控的(dedicated equipment),但其實這在試產階段(pilot lines)並不常見。因此,如果有機台得——在沒有額外檢查的情況下——同時給矽元件(Si-based devices)以及二維材料元件(MX2-based devices)使用,那麼我們就得小心避免晶圓之間的交互污染(cross-contamination)。我們必須預防新材料不會損害矽元件(Si-based devices)的效能,並且也得十分留意與避免由那些交互污染所引起的製程偏移(process drifts)。因此,對於應該使用什麼樣的二維材料,原則上我們是偏好使用已經有在晶圓廠大量使用,且有明確的化學品處理程序的材料。而這對於將矽元件以及二維材料元件整合在一起的「混合製程」(hybrid integration)更為重要。最後,化學品的安全性也是必須納入考慮的因素。

具有較高載子遷移率與化學穩定性的過渡金屬硫化物 MX2 二維材料有:二硫化鎢 WS2、二硫化鉬 MoS2、二硒化鉬 MoSe2 與二硒化鎢 WSe2。半導體製程中經常採用硫化物氣體(像是蝕刻),至於鎢 W 與鉬 Mo 則是用在中段製程居多。碲化物(Tellurides)與硒化物(selenides)的毒性較強,所以使用時得更格外小心,可能會在它的沈積及其隨後的釋氣(outgassing)被釋放到空氣中以造成危害。

大部分文獻採用的過渡金屬硫化物 MX2 二維材料是二硫化鎢 WS2 與二硫化鉬 MoS2,而這裡我們採用的是二硫化鎢 WS2,因為它的載子理論遷移率較高,雖然在整合元件上,二硫化鉬 MoS2 似乎有著較好的效能表現。

2.1. 單片奈米薄板 MX2 二維材料的製程與二維材料的選擇(Single-Sheet Process Flow and Adaptations for MX2 Material Properties)

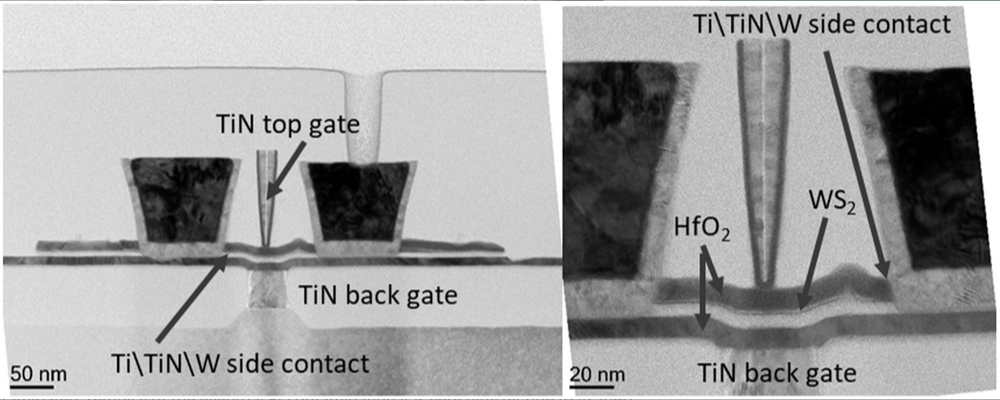

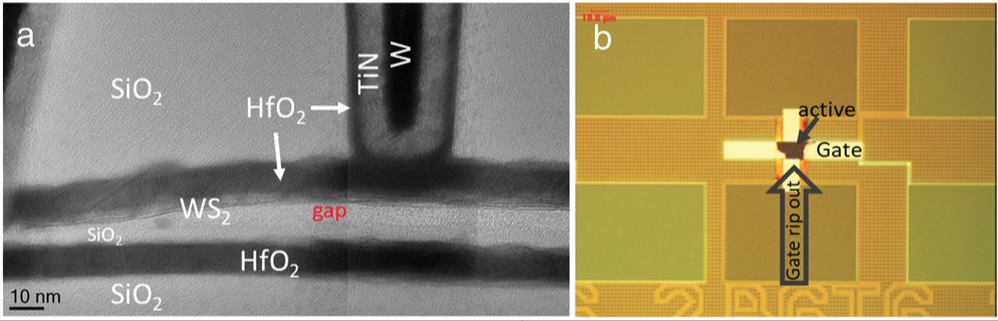

下圖二為——具有雙閘極結構的——二硫化鎢 WS2 電晶體的穿隧掃描顯影圖(in-line TEM),並且是在無塵室裡的 300-mm 晶圓上製作出來的(而非理想實驗室環境)。這種側向電極電晶體(side contacted WS2 transistor)的上下表面都有著氮化鈦 TiN 閘極與以二氧化鉿 HfO2 為基礎的閘極介電層。之所以被稱為側向電極電晶體,是因為它的汲極與源極被稱為邊緣電極(edge contact),其金屬部份(contact metal)只跟最重要的——作為電流通道的—— MX2 二維材料的晶格邊緣(crystal edge)有所接觸。

之所以採用 TiN 閘極以及兩側的 Ti\TiN 接觸電極,純粹是因為它們較能與大多數晶圓廠以及矽元件製程相容,所以在效能方面,也許還有些進步空間。例如說,像是鉍 Bi 或錫 Sn / 鉑 Pt 這些半金屬(Semimetal)就滿適合依序作為 N/PMOS 通道的接觸電極(contact metal),只不過這些材料就跟矽元件的前段製程不太相容,像是鉑 Pt 就不太能用在晶圓廠裡,因為它很可能會損害矽元件的效能,而且也很難避免晶圓之間的交互污染。一但有機台被污染了,那麼由於它本身有著非常強的惰性,所以就很難把機台裡的鉑 Pt 清理乾淨。

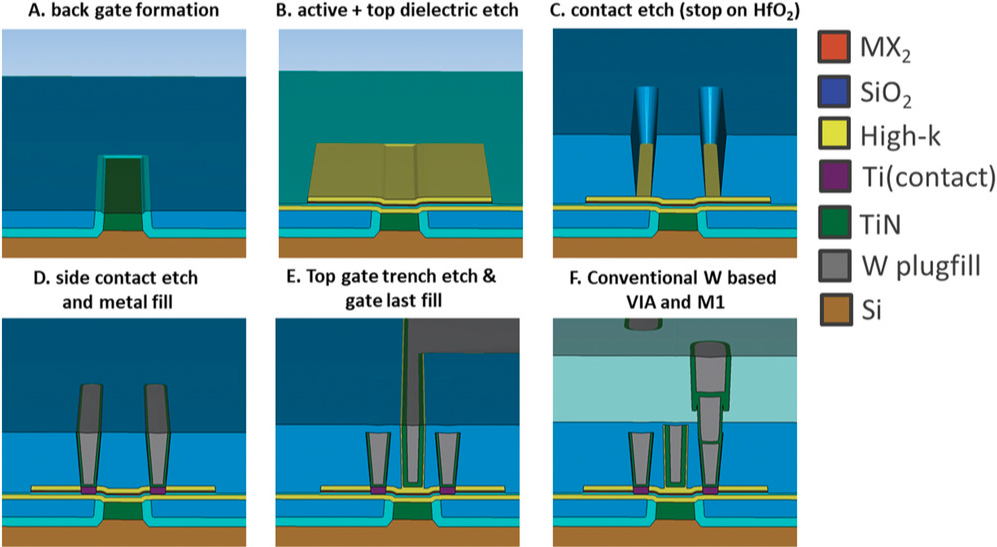

圖三為仿真製程示意圖(製程細節請詳見原文裡的引用論文)。因為過渡金屬硫化物 MX2 二維材料黏著力較差、液體可能滲入材料介面(liquid intercalation)而且厚度小於一奈米的通道實在是非常非常薄,所以我們需要非常小心地調整製程。

首先,圖三 A 為製作氮化鈦 TiN 背部電極(也就是下層閘極),接著會沈積以二氧化鉿 HfO2 為主的介電材料(dielectrics),然後才是沈積二硫化鎢 WS2 二維材料、上層介電材料以及上層閘極(top gate)。值得注意的是,如圖三 B 所示,上層閘極的介電材料(top gate dielectric)以及二硫化鎢 WS2 二維材料是同時被顯影成形的(patterened)。接著才是做兩側的接觸電極(圖三 C 與 D)。兩側接觸電極的製作方式為,首先蝕刻二氧化矽 SiO2 直到二氧化鉿 HfO2 的上表面,接著再針對接下來的二氧化鉿 HfO2 以及二硫化鎢 WS2 二維材料本身蝕刻,其中,二氧化鉿 HfO2 就是上方閘極的高介電係數介電材料(the top high-k)。最後再於接觸電極的槽溝(contact trench)依序填入鈦 Ti、氮化鈦 TiN 與鎢 W 金屬,再用化學研磨(CMP)把大家磨平,磨平後即為圖三 D。在處理完兩側金屬接觸後,才接著來製作上層閘極,這種製程稱為「閘極後製法」(gate-last top gate process)。如圖三 E 所示,先於二氧化矽 SiO2 蝕刻出一個槽溝,同樣是蝕刻到上層二氧化鉿 HfO2 為止。照理來說這時應該要開始沈積金屬,但在那之前,我們先再次沈積一層二氧化鉿 HfO2,以避免上層閘極與其底下的電流通道(二硫化鎢 WS2)之間發生短路。沈積完二氧化鉿 HfO2 之後,才接著沈積氮化鈦 TiN 與鎢 W 金屬。值得注意的是,兩側金屬電極以及上層閘極都是採用業界標準的嵌入製程(damascene approach)。

如前所述,我們的製程必須慎重考慮過渡金屬硫化物 MX2 二維材料的各種化學性質。由於蝕刻二硫化鎢 WS2 薄膜的選擇比相當有限,所以我們選擇同時蝕刻二硫化鎢 WS2 與二氧化鉿 HfO2。我們可以把二氧化鉿 HfO2 作為一層保護罩,讓二氧化鉿 HfO2 保護二硫化鎢 WS2 的單原子層,以免它在後續的蝕刻時被氧化或是破壞。而由於液體相當容易滲入(liquid intercalation)二硫化鎢 WS2 與二氧化鉿 HfO2 的夾層中(delamination),所以沒辦法在製作完主動區、金屬電極以及上層閘極之後,直接使用濕蝕刻製程。而且如果直接使用濕蝕刻,那可能也會在其他面積較小的主動區,造成材料的斷裂或是剝落脫離(lift-off)等現象。一般來說,我們要避免 MX2 二維材料的邊緣裸露出來,以免被濕蝕刻破壞。所以,只有在 MX2 二維材料邊緣被其他材料覆蓋保護的時候,我們才會使用濕蝕刻製程。

至於另一個需要注意的點,則是所謂的「乾裂」現象(non-liquid-intercalation-based delamination),也就是説,這種分層現象(delamination)並不是由液體造成的。之所以發生乾裂,主要是因為 MX2 二維材料與其周圍物質的凡德瓦力相當薄弱——相較於那些常用在矽元件製程的材料。圖四 A 展示了長度一微米(1um)的二硫化鎢 WS2 通道,此通道與其底部的二氧化矽 SiO2 之間裂開來了。此乾裂是我們在使用雙向離子束銑削(double-sided ion beam milling)以製作電子穿隧顯影(TEM)樣本的時候所發生的,這恰好說明了過渡金屬硫化物 MX2 與其周圍材料相當薄弱的鍵結力。

不過,也多虧了 MX2 較差的黏性,使得與它相接觸的材料並不會承受太大的應力(stress)或是形變(strain)。因為如果應力太大,那剪力(shear force)就會太大,就可能使得 MX2 與周圍材料分離,所以我們在顯影成形(patterning)主動區時,也採用了應力較小的 SOC(Spin-On-Carbon) 或是 SOG (Spin-On-Glass)作為遮罩(hard mask),以取代——通常用於成形小面積元件的——氧化層遮罩。也因為應力所引起的力量與表面積正相關,所以在整片 300-mm 晶圓塗滿大面積 MX2 ,以準備替主動區曝光顯影成形的時候,是二維材料最容易斷裂的時候。總之,MX2 的塗抹面積越小越好。

除了圖四 A 的乾裂現象,我們也有觀察到大面積閘極被化學研磨磨掉的問題,如圖四 B 所示。雖然這對面積較小的電晶體來說不太會是問題,但對大面積元件來說可能會有些製程問題。總之,我們在設計每一道製程時,都得仔細考慮到可能的材料斷裂剝落問題。例如說,我們為了避免氮化矽(SiN)對周圍元件造成的高壓力導致材料斷裂,我們目前的製程就沒有使用任何氮化矽側壁(spacer)。

整體而言,最為關鍵的三道製程為:(1) MX2 的成長與顯影成形、(2) 高介電值絕緣材料(high-k dielectric)的沉積以及 (3) 作為源極與汲極的接觸電極的製作。接下來我們會說明以上這三道關鍵製程的研發進展,並說明我們究竟還缺少了什麼,才能把整個製程做到理想。我們預期未來的單原子層——或頂多雙原子層——的 MX2 元件,一定會需要約 1nm 的等效氧化層厚度(EOT)高介電值絕緣材料,以及電阻小於 100 Ω µm 的接觸電極。

2.2. MX2 二維材料的成長與顯影成形(MX2 Growth and Patterning)

如果想要足夠有效地控制電流通道,那麼二維材料組成的通道最多只能有兩層原子層。而且二維材料的能帶結構也與原子層數有關。總而言之,我們需要能用來成長單或雙原子層 MX2 的沉積方法。

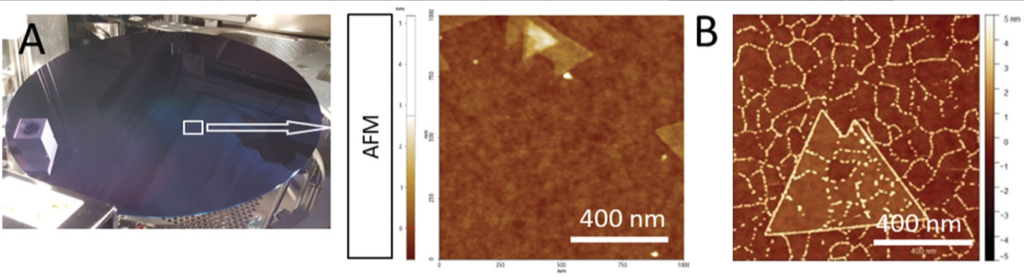

能直接用在整片晶圓,並且適合與其他製程整合在一起的沈積方法被稱為「全片沉積法」(blanket full wafer depositions)。這種沈積法還滿多的,但目前最適合沉積整片晶圓的方法是化學氣相沉積法(Chemical Vapor Deposition; CVD)。理想上,單層 MX2 或是雙層 MX2 能夠均勻地被沈積在直徑長達 300 毫米(也就是 30 公分,12 英吋)的整片晶圓上。不過,實際上化學沈積出來的結果一定是不太均勻。有些地方有著較厚的多晶 MX2,有些地方則比較少也較薄。圖五 A 為使用 W(CO)6 與 H2S 有機化學氣體分子沈積出來的二硫化鎢 WS2 樣貌,並且是沈積在整片直徑 300 毫米的晶圓上。如果第一層 MX2 的晶粒邊界(grain boundaries)恰好落於元件主動區範圍內,那就會影響元件的載子遷移率。因此,大部分的二維材料化學沈積研究都聚焦於該如何增加第一層原子層的晶粒大小,以盡可能減少會造成載子散射從而降低載子遷移率的晶粒邊界。而為了能在整片晶圓上直接一次沈積完成, MX2 多晶形體(polycrystallinity)的形成是相當難避免的。但因為太厚的 MX2 也會影響到元件電性,所以還是得盡力避免,至少得保證不會對良率影響太多。如果部分 WS2 在第一層成長結束時恰好成核結晶了(nucleation),那麼再接著長第二層的時候,第一層已成核的 WS2 就會成長得更快速,使其在第二層長完時長得更厚。

想要在擁有足夠大的晶粒的同時,還要能避免長得太厚,會是製作 MX2 二維材料元件最為關鍵的挑戰。也就是說,必須要能夠精準控制 MX2 的成核速度與水平成長速度,相關的製程參數為溫度、壓力、時間以及化學沈積前驅物(precursor)的選擇。溫度越高,MX2 晶體就長得越大。而低溫的晶粒則會比較小,但卻會發現有一些晶體會長得特別高(out-of-plane),反而似乎長得太超過。而如果使用原子沈積法(Atomic Layer Deposition; ALD),那成長溫度可以更低,但這不僅會使晶粒變得更小(散射得更嚴重,電阻從而變得更大),而且也更難抑制 MX2 晶體的過度成長。至於前驅物,它必須被調整得既能有效抑制 MX2 的過度成長(overgrowth),而又有助於 MX2 晶體的側向成長(lateral growth)。

因為溫度越高,就越有可能破壞已做好的電路構造,像是使晶圓彎曲或是一些物質的結晶化(crystallization),所以整道製程可允許的溫度上限就與目前這一步製程以前的所有製程,以及跟該電路將來的操作環境有關。以二維材料的後段製程(BEOL)來說,其溫度最高應可達到 500 °C,至於前段製程(FEOL)則能容許再稍微高一點的溫度。

還有一個能增加晶粒尺寸(grain size)的方法,那就是把 MX2 沈積在一個已經擁有較大晶粒的晶體基板上(crystalline template substrate),像是主成份為氧化鋁(Al2O3)的石英(sapphire),但這也意味著我們得設法將於石英上成長完的 MX2 轉移搬遷到 300-mm 的目標晶圓上。目前的方法 [37] 基本上是先把 MX2 轉移到玻璃晶圓上(glass wafer),然後再轉移到目標晶圓上。目前業界已有 300-mm 的藍寶石晶圓,所以目前的確能夠在整片晶圓上成長 MX2 以加大晶粒尺寸。雖然通常我們不會考慮這種要在 300-mm 晶圓上轉移搬遷 MX2 的製程,但也許可以用在一些比較特殊規格的製程上,像是之前提到的將矽元件與單片(single-sheet)二維材料混合在一起的製程上,因為其表面可能較為平坦光滑,所以就也比較適合需要轉移搬遷 MX2 的製程。但如果是要給能承受較高沈積溫度的邏輯元件製程,那直接在目標晶圓上沉積 MX2 應該是比較好的作法。

最大的問題還是在於該怎麼從石英晶圓把 MX2 轉移搬遷至目標晶圓上:每一道製程本身的複雜性、在整片晶圓上的均勻性、容易受雜質顆粒影響的特性以及最後的表面清洗,這一切都使得在石英晶圓上成長 MX2 的作法相當困難。而假如目標晶圓本身已經被顯影成形了(pre-patterened wafers),那麼那些如階梯狀的邊緣都可能會在剛轉移過來的 MX2 薄膜上產生空洞或讓它直接斷裂。而就算使用 CMP 磨平目標晶圓,也很難完全去除一些在不同材料介面上的鉛直稜角。

假如不論是直接沈積,還是先成長在別的樣板晶圓上然後再搬移到目標晶圓,都無法長出足夠大的晶粒的話,那也許可以考慮使用晶種來長晶(seeded localized growth)。雖然這種「晶種長晶法」就沒辦法一次涵蓋整片晶圓,但還是會盡可能使用有助於側向成長(lateral grain growth)的製程條件,以設法加大晶體顆粒,覆蓋整片晶圓。通常放在元件或是電路中間的晶種(seed)是用在特定位置上的[1][14]。或是說,MX2 可以長在金屬電極上,直接把金屬電極作為晶種(seed)[20][21]。對於不需要太大晶體尺寸的微縮製程,這方法也許可行,但缺點就在於可能會減少整片晶圓的有效面積。如果基板不具有晶體結構(amorphous),那麼在它上面的晶體成長就會比較沒有規則,所以能作為元件或是電路的晶圓區域,就只能受限於成長良好的晶體的內切圓內側了。

請問IEDM Paper 7.4 Nearly Ideal Subthreshold Swing in Monolayer MoS2 Top-Gate nFETs with Scaled EOT of 1nm)中有提到ILX是什麼材料嗎